Os dispositivos de potência semicondutores ocupam uma posição central nos sistemas eletrónicos de potência, especialmente no contexto do rápido desenvolvimento de tecnologias como a inteligência artificial, as comunicações 5G e os novos veículos energéticos, os requisitos de desempenho para os mesmos foram melhorados.

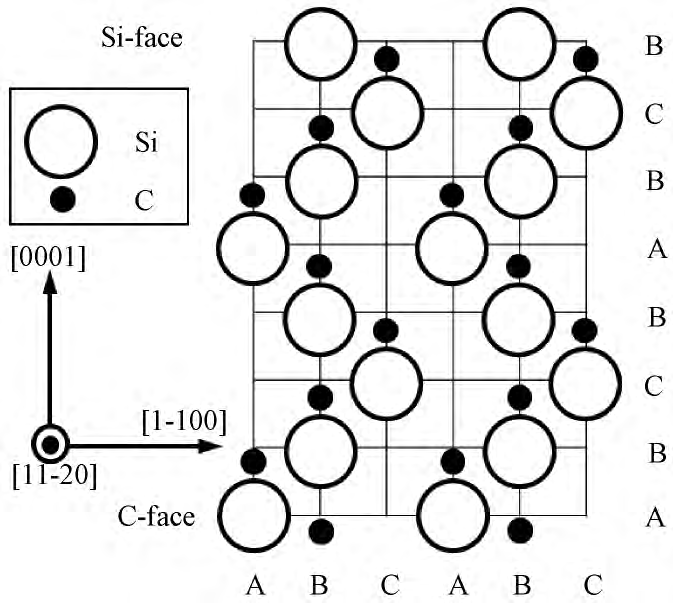

Carboneto de silício(4H-SiC) tornou-se um material ideal para a fabricação de dispositivos de energia semicondutores de alto desempenho devido às suas vantagens, como amplo bandgap, alta condutividade térmica, alta intensidade de campo de ruptura, alta taxa de deriva de saturação, estabilidade química e resistência à radiação. No entanto, o 4H-SiC possui alta dureza, alta fragilidade, forte inércia química e alta dificuldade de processamento. A qualidade da superfície do seu wafer de substrato é crucial para aplicações de dispositivos em larga escala.

Portanto, melhorar a qualidade da superfície dos wafers de substrato 4H-SiC, especialmente removendo a camada danificada na superfície de processamento do wafer, é a chave para obter um processamento de wafer de substrato 4H-SiC eficiente, de baixa perda e de alta qualidade.

Experimentar

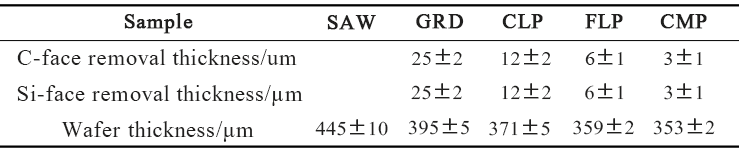

O experimento usa um lingote 4H-SiC tipo N de 4 polegadas cultivado pelo método de transporte físico de vapor, que é processado por meio de corte de fio, retificação, retificação áspera, retificação fina e polimento, e registra a espessura de remoção da superfície C e da superfície Si. e a espessura final do wafer em cada processo.

Figura 1 Diagrama esquemático da estrutura cristalina 4H-SiC

Figura 2 Espessura removida do lado C e do lado Si de 4H-Bolacha de SiCapós diferentes etapas de processamento e espessura do wafer após o processamento

A espessura, morfologia da superfície, rugosidade e propriedades mecânicas do wafer foram totalmente caracterizadas pelo testador de parâmetros de geometria do wafer, microscópio de interferência diferencial, microscópio de força atômica, instrumento de medição de rugosidade superficial e nanoindenter. Além disso, um difratômetro de raios X de alta resolução foi utilizado para avaliar a qualidade do cristal do wafer.

Estas etapas experimentais e métodos de teste fornecem suporte técnico detalhado para estudar a taxa de remoção de material e a qualidade da superfície durante o processamento de 4H-Bolachas de SiC.

Por meio de experimentos, os pesquisadores analisaram as mudanças na taxa de remoção de material (MRR), na morfologia e na rugosidade da superfície, bem como nas propriedades mecânicas e na qualidade do cristal do 4H-Bolachas de SiCem diferentes etapas de processamento (corte de fio, desbaste, desbaste, desbaste fino, polimento).

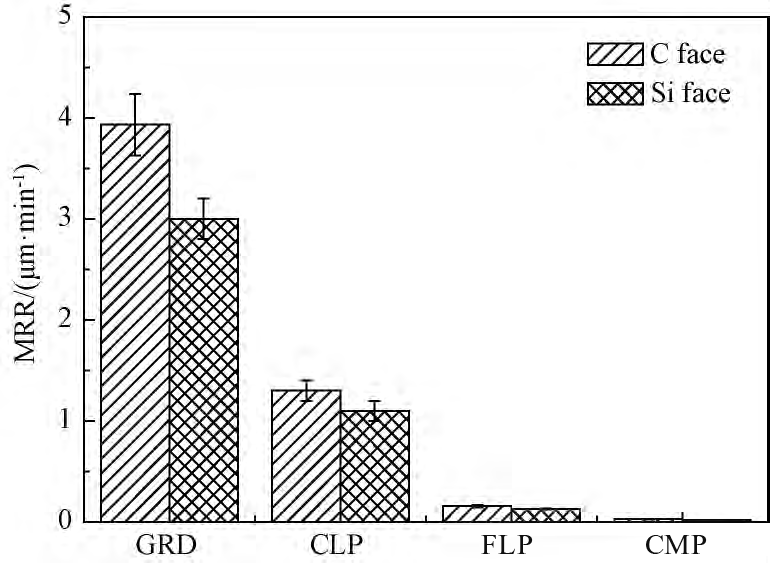

Figura 3 Taxa de remoção de material da face C e face Si de 4H-Bolacha de SiCem diferentes etapas de processamento

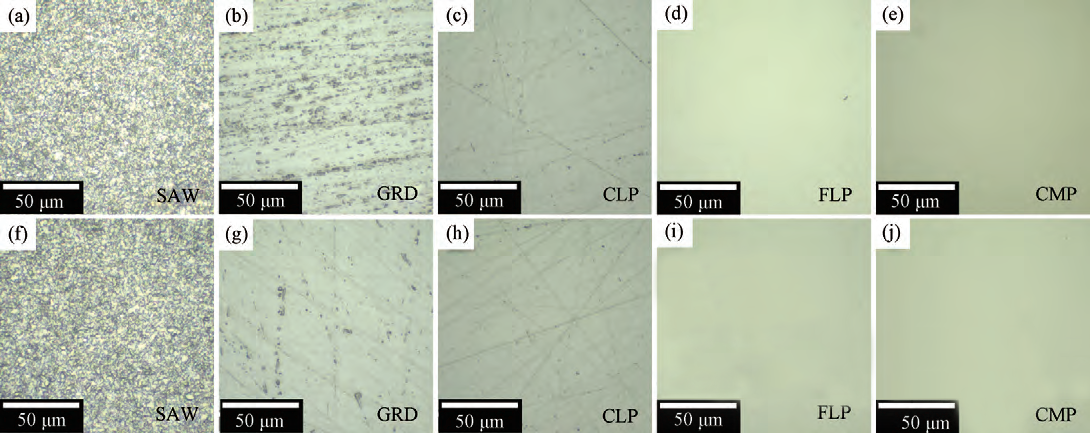

O estudo descobriu que devido à anisotropia das propriedades mecânicas de diferentes faces cristalinas de 4H-SiC, há uma diferença no MRR entre a face C e a face Si sob o mesmo processo, e o MRR da face C é significativamente maior do que o de Si-face. Com o avanço das etapas de processamento, a morfologia superficial e a rugosidade dos wafers 4H-SiC são gradualmente otimizadas. Após o polimento, o Ra da face C é de 0,24 nm, e o Ra da face Si atinge 0,14 nm, o que pode atender às necessidades de crescimento epitaxial.

Figura 4 Imagens de microscópio óptico da superfície C (a~e) e superfície Si (f~j) do wafer 4H-SiC após diferentes etapas de processamento

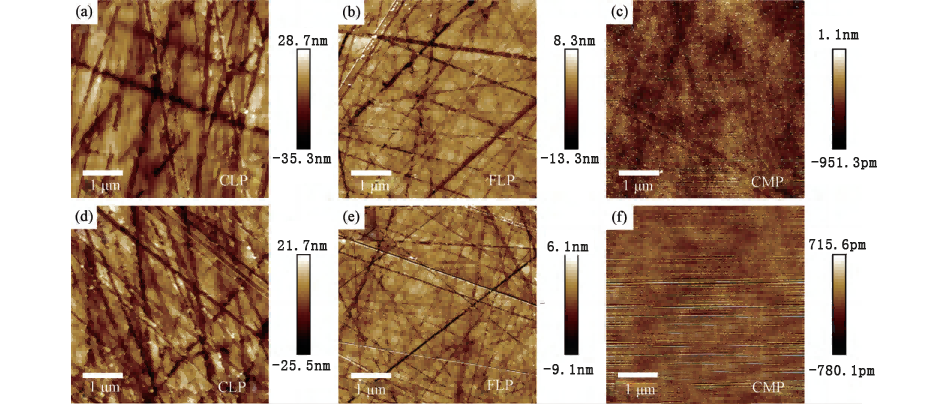

Figura 5 Imagens de microscópio de força atômica da superfície C (a~c) e superfície Si (d~f) do wafer 4H-SiC após etapas de processamento CLP, FLP e CMP

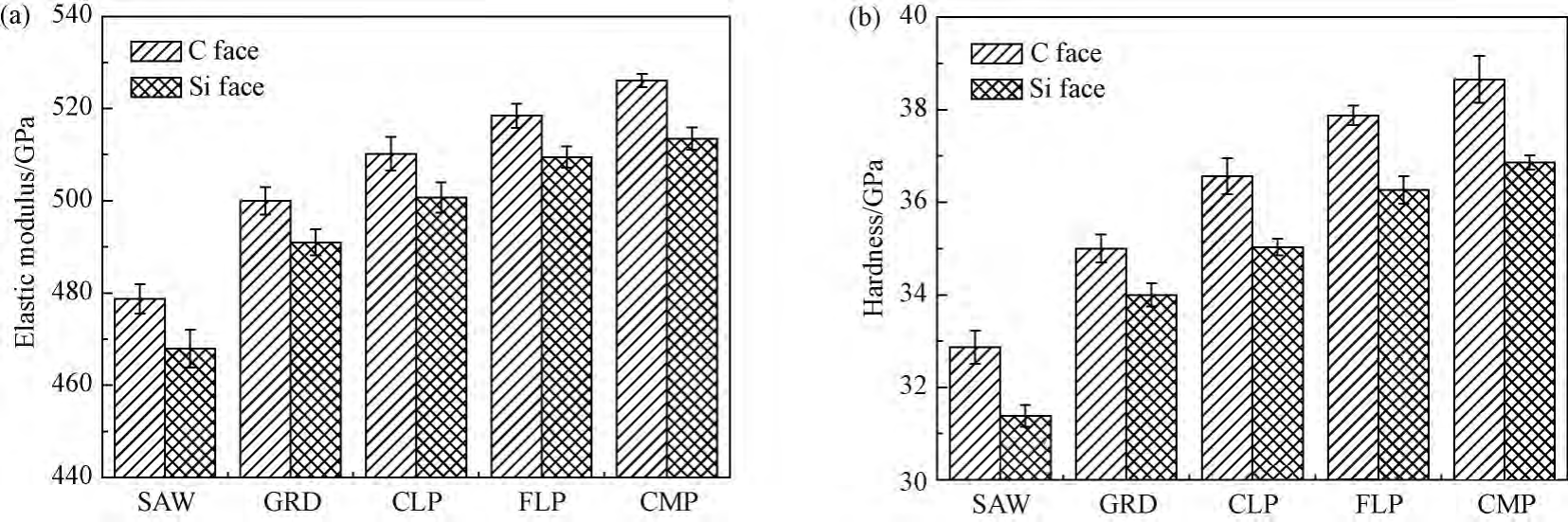

Figura 6 (a) módulo de elasticidade e (b) dureza da superfície C e superfície Si do wafer 4H-SiC após diferentes etapas de processamento

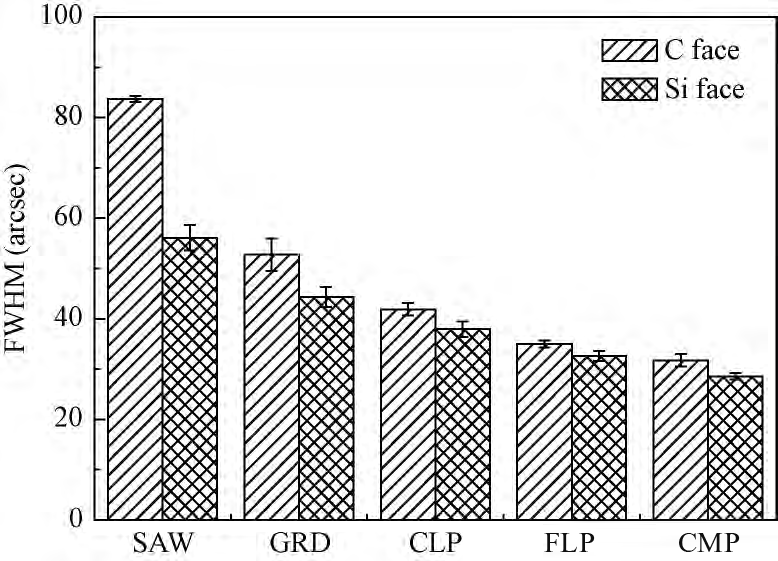

O teste de propriedades mecânicas mostra que a superfície C do wafer tem menor tenacidade do que o material da superfície Si, um maior grau de fratura frágil durante o processamento, remoção de material mais rápida e morfologia e rugosidade superficial relativamente pobres. Remover a camada danificada na superfície processada é a chave para melhorar a qualidade da superfície do wafer. A largura de meia altura da curva de balanço 4H-SiC (0004) pode ser usada para caracterizar e analisar de forma intuitiva e precisa a camada de dano superficial do wafer.

Figura 7 (0004) curva oscilante de meia largura da face C e face Si do wafer 4H-SiC após diferentes etapas de processamento

Os resultados da pesquisa mostram que a camada de dano superficial do wafer pode ser gradualmente removida após o processamento do wafer 4H-SiC, o que melhora efetivamente a qualidade da superfície do wafer e fornece uma referência técnica para processamento de alta eficiência, baixa perda e alta qualidade. de wafers de substrato 4H-SiC.

Os pesquisadores processaram wafers 4H-SiC por meio de diferentes etapas de processamento, como corte de fio, retificação, retificação grosseira, retificação fina e polimento, e estudaram os efeitos desses processos na qualidade da superfície do wafer.

Os resultados mostram que com o avanço das etapas de processamento, a morfologia superficial e a rugosidade do wafer são gradativamente otimizadas. Após o polimento, a rugosidade da face C e da face Si atinge 0,24 nm e 0,14 nm respectivamente, o que atende aos requisitos de crescimento epitaxial. A face C do wafer tem menor tenacidade do que o material da face Si e é mais propensa a fraturas frágeis durante o processamento, resultando em morfologia superficial e rugosidade relativamente pobres. Remover a camada de dano superficial da superfície processada é a chave para melhorar a qualidade da superfície do wafer. A meia largura da curva de balanço 4H-SiC (0004) pode caracterizar de forma intuitiva e precisa a camada de dano superficial do wafer.

A pesquisa mostra que a camada danificada na superfície dos wafers 4H-SiC pode ser gradualmente removida por meio do processamento do wafer 4H-SiC, melhorando efetivamente a qualidade da superfície do wafer, fornecendo uma referência técnica para alta eficiência, baixa perda e alta - processamento de qualidade de wafers de substrato 4H-SiC.

Horário da postagem: 08/07/2024