O Wafer Silicon On Insulator (SOI) da Semicera está na vanguarda da inovação em semicondutores, oferecendo isolamento elétrico aprimorado e desempenho térmico superior. A estrutura SOI, que consiste em uma fina camada de silício sobre um substrato isolante, oferece benefícios críticos para dispositivos eletrônicos de alto desempenho.

Nossos wafers SOI são projetados para minimizar a capacitância parasita e as correntes de fuga, o que é essencial para o desenvolvimento de circuitos integrados de alta velocidade e baixa potência. Esta tecnologia avançada garante que os dispositivos operem de forma mais eficiente, com maior velocidade e menor consumo de energia, crucial para a eletrónica moderna.

Os avançados processos de fabricação empregados pela Semicera garantem a produção de wafers SOI com excelente uniformidade e consistência. Essa qualidade é vital para aplicações em telecomunicações, automotiva e eletrônica de consumo, onde são necessários componentes confiáveis e de alto desempenho.

Além de seus benefícios elétricos, os wafers SOI da Semicera oferecem isolamento térmico superior, melhorando a dissipação de calor e a estabilidade em dispositivos de alta densidade e alta potência. Esse recurso é particularmente valioso em aplicações que envolvem geração significativa de calor e exigem gerenciamento térmico eficaz.

Ao escolher o Silicon On Insulator Wafer da Semicera, você investe em um produto que apoia o avanço de tecnologias de ponta. Nosso compromisso com a qualidade e a inovação garante que nossos wafers SOI atendam às rigorosas demandas da indústria de semicondutores atual, fornecendo a base para dispositivos eletrônicos de próxima geração.

| Unid | Produção | Pesquisar | Fictício |

| Parâmetros de Cristal | |||

| Politipo | 4H | ||

| Erro de orientação de superfície | <11-20 >4±0,15° | ||

| Parâmetros Elétricos | |||

| Dopante | Nitrogênio tipo n | ||

| Resistividade | 0,015-0,025ohm·cm | ||

| Parâmetros Mecânicos | |||

| Diâmetro | 150,0±0,2 mm | ||

| Grossura | 350±25 μm | ||

| Orientação plana primária | [1-100]±5° | ||

| Comprimento plano primário | 47,5±1,5 mm | ||

| Apartamento secundário | Nenhum | ||

| TTV | ≤5 μm | ≤10 μm | ≤15 μm |

| LTV | ≤3 μm(5mm*5mm) | ≤5 μm(5mm*5mm) | ≤10 μm(5mm*5mm) |

| Arco | -15μm ~ 15μm | -35μm ~ 35μm | -45μm ~ 45μm |

| Urdidura | ≤35 μm | ≤45 μm | ≤55 μm |

| Rugosidade frontal (Si-face) (AFM) | Ra≤0,2nm (5μm*5μm) | ||

| Estrutura | |||

| Densidade de microtubos | <1 ea/cm2 | <10 ea/cm2 | <15 ea/cm2 |

| Impurezas metálicas | ≤5E10átomos/cm2 | NA | |

| DBP | ≤1500 ea/cm2 | ≤3000 ea/cm2 | NA |

| TSD | ≤500 ea/cm2 | ≤1000 ea/cm2 | NA |

| Qualidade frontal | |||

| Frente | Si | ||

| Acabamento de superfície | CMP de face Si | ||

| Partículas | ≤60ea/wafer (tamanho≥0,3μm) | NA | |

| Arranhões | ≤5ea/mm. Comprimento cumulativo ≤Diâmetro | Comprimento cumulativo≤2*Diâmetro | NA |

| Casca de laranja/caroços/manchas/estrias/rachaduras/contaminação | Nenhum | NA | |

| Lascas/reentrâncias/fraturas/placas sextavadas nas bordas | Nenhum | ||

| Áreas politípicas | Nenhum | Área acumulada≤20% | Área acumulada≤30% |

| Marcação a laser frontal | Nenhum | ||

| Qualidade traseira | |||

| Acabamento traseiro | CMP face C | ||

| Arranhões | ≤5ea/mm, comprimento cumulativo≤2*Diâmetro | NA | |

| Defeitos traseiros (lascas/recortes nas bordas) | Nenhum | ||

| Rugosidade nas costas | Ra≤0,2nm (5μm*5μm) | ||

| Marcação a laser traseira | 1 mm (da borda superior) | ||

| Borda | |||

| Borda | Chanfro | ||

| Embalagem | |||

| Embalagem | Epi-pronto com embalagem a vácuo Embalagem cassete multi-wafer | ||

| *Observações: "NA" significa sem solicitação. Itens não mencionados podem referir-se ao SEMI-STD. | |||

-

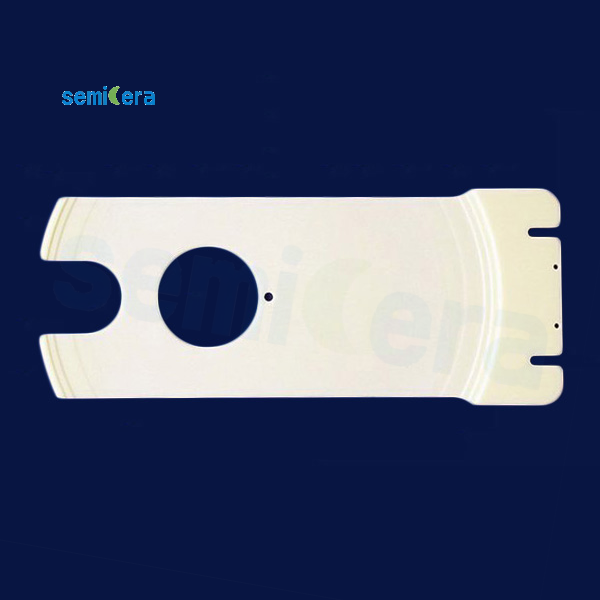

Garfo cerâmico semicondutor de zircônia

-

Susceptor de wafer de grafite com revestimento SiC

-

Barco wafer de carboneto de silício de grau premium para cr...

-

Barco wafer de carboneto de silício

-

Aquecedor elétrico de grafite personalizado com forno a vácuo

-

Susceptor de barril revestido com carboneto de silício