Os substratos de wafer polido de dupla face SiC semi-isolante de alta pureza (HPSI) de 4 polegadas da Semicera são criados para atender às demandas exatas da indústria de semicondutores. Esses substratos são projetados com planicidade e pureza excepcionais, oferecendo uma plataforma ideal para dispositivos eletrônicos de última geração.

Esses wafers HPSI SiC se distinguem por sua condutividade térmica superior e propriedades de isolamento elétrico, tornando-os uma excelente escolha para aplicações de alta frequência e alta potência. O processo de polimento bilateral garante rugosidade superficial mínima, o que é crucial para melhorar o desempenho e a longevidade do dispositivo.

A alta pureza dos wafers de SiC da Semicera minimiza defeitos e impurezas, levando a maiores taxas de rendimento e confiabilidade do dispositivo. Esses substratos são adequados para uma ampla gama de aplicações, incluindo dispositivos de micro-ondas, eletrônica de potência e tecnologias LED, onde precisão e durabilidade são essenciais.

Com foco na inovação e qualidade, a Semicera utiliza técnicas avançadas de fabricação para produzir wafers que atendem aos rigorosos requisitos da eletrônica moderna. O polimento dupla face não só melhora a resistência mecânica, mas também facilita uma melhor integração com outros materiais semicondutores.

Ao escolher os substratos de wafer polidos de dupla face HPSI SiC semi-isolantes de alta pureza de 4 polegadas da Semicera, os fabricantes podem aproveitar os benefícios do gerenciamento térmico aprimorado e do isolamento elétrico, abrindo caminho para o desenvolvimento de dispositivos eletrônicos mais eficientes e potentes. Semicera continua a liderar a indústria com seu compromisso com a qualidade e o avanço tecnológico.

| Unid | Produção | Pesquisar | Fictício |

| Parâmetros de Cristal | |||

| Politipo | 4H | ||

| Erro de orientação de superfície | <11-20 >4±0,15° | ||

| Parâmetros Elétricos | |||

| Dopante | Nitrogênio tipo n | ||

| Resistividade | 0,015-0,025ohm·cm | ||

| Parâmetros Mecânicos | |||

| Diâmetro | 150,0±0,2 mm | ||

| Grossura | 350±25 μm | ||

| Orientação plana primária | [1-100]±5° | ||

| Comprimento plano primário | 47,5±1,5 mm | ||

| Apartamento secundário | Nenhum | ||

| TTV | ≤5 μm | ≤10 μm | ≤15 μm |

| LTV | ≤3 μm(5mm*5mm) | ≤5 μm(5mm*5mm) | ≤10 μm(5mm*5mm) |

| Arco | -15μm ~ 15μm | -35μm ~ 35μm | -45μm ~ 45μm |

| Urdidura | ≤35 μm | ≤45 μm | ≤55 μm |

| Rugosidade frontal (Si-face) (AFM) | Ra≤0,2nm (5μm*5μm) | ||

| Estrutura | |||

| Densidade de microtubos | <1 ea/cm2 | <10 ea/cm2 | <15 ea/cm2 |

| Impurezas metálicas | ≤5E10átomos/cm2 | NA | |

| DBP | ≤1500 ea/cm2 | ≤3000 ea/cm2 | NA |

| TSD | ≤500 ea/cm2 | ≤1000 ea/cm2 | NA |

| Qualidade frontal | |||

| Frente | Si | ||

| Acabamento de superfície | CMP de face Si | ||

| Partículas | ≤60ea/wafer (tamanho≥0,3μm) | NA | |

| Arranhões | ≤5ea/mm. Comprimento cumulativo ≤Diâmetro | Comprimento cumulativo≤2*Diâmetro | NA |

| Casca de laranja/caroços/manchas/estrias/rachaduras/contaminação | Nenhum | NA | |

| Lascas/reentrâncias/fraturas/placas sextavadas nas bordas | Nenhum | ||

| Áreas politípicas | Nenhum | Área acumulada≤20% | Área acumulada≤30% |

| Marcação a laser frontal | Nenhum | ||

| Qualidade traseira | |||

| Acabamento traseiro | CMP face C | ||

| Arranhões | ≤5ea/mm, comprimento cumulativo≤2*Diâmetro | NA | |

| Defeitos traseiros (lascas/recortes nas bordas) | Nenhum | ||

| Rugosidade nas costas | Ra≤0,2nm (5μm*5μm) | ||

| Marcação a laser traseira | 1 mm (da borda superior) | ||

| Borda | |||

| Borda | Chanfro | ||

| Embalagem | |||

| Embalagem | Epi-pronto com embalagem a vácuo Embalagem cassete multi-wafer | ||

| *Observações: "NA" significa sem solicitação. Itens não mencionados podem referir-se ao SEMI-STD. | |||

-

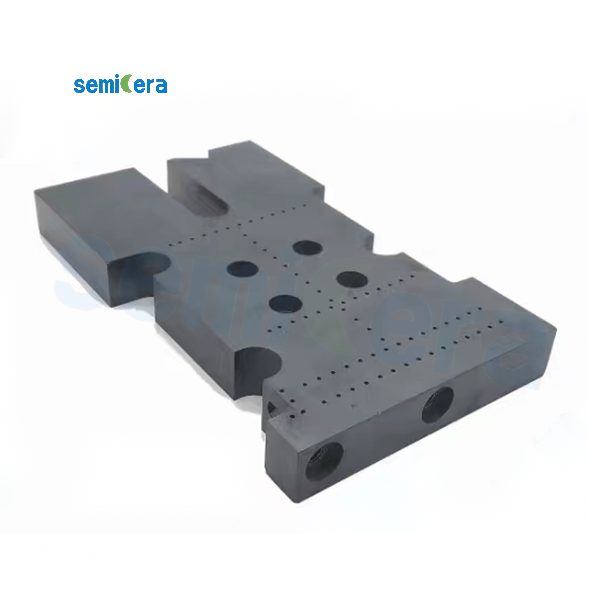

As peças estruturais de carboneto de silício podem ser personalizadas

-

Cobertura de grafite revestida com carboneto de tântalo (TaC)

-

4″ 6″ 8″ Condutivo e Se...

-

Aquecedor de substrato semicondutor MOCVD MOCVD...

-

Acessórios de grafite para campo quente de single cr...

-

Material de isolamento de feltro de grafite flexível